李森,李中,袁强,唐建

(中国兵器装备集团自动化研究所有限公司 特种计算机事业部,四川 绵阳 621000)

随着国产处理器在各种电子设备中的应用越来越广泛,以国产CPU 龙芯系列为主的各种计算机不断得到普及,但龙芯系列芯片自带的UART 接口有限,在计算机硬件系统的设计中常常需要使用FPGA(Field Programmable Gate Array)或CPLD(Complex Programmable Logic Device)扩展多路串口[1],以满足设计需要。但Xilinx 官方[2]的UART IP核为AXI(Advanced eXtensible Interface)总线接口,操作比较繁琐,不能直接与Local IO 接口适配。为了解决与龙芯Local IO 接口适配以及UART 接口参数可在线配置的问题,本文设计了一种基于Local IO 接口的UART IP核,能够实现串口协议参数、中断系统参数在线配置功能,解决了龙芯系列CPU 在系统设计中的串口扩增问题,增强了龙芯CPU 的兼容性。

UART IP 核由发送模块(UART_TX)、接收模块(UART_RX)、发送FIFO(TX_FIFO)、接收FIFO(RX_FIFO)、时钟模块(UART_CLK)、中断系统(UART_INTR_CTRL)、配置模块(UART_CONFIG)、Local IO 模块8 部分组成[3],如图1 所示。

图1 UART IP 整体结构Figure 1 Overall structure of UART IP

2.1 发送模块UART_TX 设计

UART IP 核的发送模块主要实现将待发送的并行数据按照串口协议转化为串行数据,并将串行数据发送到总线上,该发送模块具有数据位长度、奇偶校验、停止位长度可配置的功能。其关键端口的具体设计如下:

(1)data_length [1:0]:数据位长度配置,2’b00(5bit)、2’b01(6bit)、2’b10(7bit)、2’b11(8bit),数据位长度默认为8bit。

(2)parity_set[1:0]:校验位设置,2’b11(奇校验)、2’b10(偶校验)、2’b00(无校验),默认为无校验。

(3)stop_length [1:0]:停止位长度设置,2’b11(2bit)、2’b10(1.5bit)、2’b00(1bit),默认停止位长度为1bit。

(4)data_in[7:0]:8bit 并行数据输入。

(5)tx_out:串口发送器,串行数据输出。

按照以上设计思路,对UART 发送模块设计实现,并进行仿真验证。如图2 所示为data_length=2’b11、parity_set=2’b10、stop_length=2’b00、data_in=8’b10110011 以及data_length=2’b10、parity_set=2’b11、stop_length=2’b00、data_in=8’b1001010的仿真结果。由仿真结果可知,设计正确。

图2 UART_TX 仿真结果Figure 2 UART_ TX simulation results

2.2 接收模块UART_RX 设计

UART IP 核的接收模块主要实现将串行数据按照串口协议与预设的波特率转化为并行数据输出[4]。当检测到总线上有起始位产生时,按照设定的波特率与配置模式,对总线数据进行采样。由于串口总线在空闲时保持为高,而停止位也为高电平,因此在设计接收模块的状态机中,当接收完数据位与校验位后就直接跳转到空闲态,等待下一帧串口数据的起始位。其关键端口的具体设计如下:

(1)data_length [1:0]:数据位长度配置,2’b00(5bit)、2’b01(6bit)、2’b10(7bit)、2’b11(8bit),数据位长度默认为8bit。

(2)parity_set[1:0]:校验位设置,2’b11(奇校验)、2’b10(偶校验)、2’b00(无校验),默认为无校验。

(3)rx_in:串口接收模块,串行数据输入端口。

(4)data_out[7:0]:串口接收器并行数据输出。

(5)parity_error:校验错误为1,校验正确为0。

按照以上设计思路,对UART 接收模块设计实现,并进行仿真验证。如图3 所示为data_length=2’b11、parity_set=2’b10 以 及data_length=2’b10、parity_set=2’b10 的仿真结果。其中send_data为发送的测试数据,data_out 为接收到的数据,parity_error 为接收的校验脉冲,parity_error=1’b0 表示校验正确,parity_error=1’b1 表示校验错误。由仿真结果可知,设计正确。

图3 UART_RX 模块仿真结果Figure 3 UART_ RX module simulation results

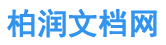

2.3 时钟模块UART_CLK 设计

为了增强IP 核扩展的灵活性,在设计时采用模块化设计的思想,将发送器与接收器使用的波特率时钟设计为一个独立的模块,以便对时钟模块进行修改时不会影响系统中其他模块的功能[5]。时钟模块实现在UART_TX 发送数据时,使输出数据按照设定的波特率输出,发送时钟设计为占空比为50%的时钟信号;

在UART_RX 接收数据时,在接收时钟的控制下对总线上的数据进行采样,接收时钟设计为每个波特率时钟周期产生一个系统时钟周期高脉冲的时钟。UART_CLK 模块的关键端口设计如下:

(1)baud_set[15:0]:波特率设置的数据输入端口,用于设置发送时钟与接收时钟的波特率大小。baud_set 的计算公式为:baud_set=0.5 fclk/Baud,其中fclk 为FPGA 的系统时钟,单位为Hz;

Baud 为串口的波特率,单位为bps。

(2)rx_in_reg:串口接收端口下降沿检测输入端口。串口处于空闲时,当检测到该接口为1时,就立刻产生接收时钟,从uart_rx_clk 端口输出。

(3)receive_done:串口每一帧数据接收完毕的脉冲信号输入。当检测到该信号为1时,就结束uart_rx_clk 时钟的输出。

(4)uart_tx_clk:串口发送时钟的输出端口。

(5)uart_rx_clk:串口接收时钟的输出端口。

按照以上设计思路,对UART_CLK 模块设计实现,并进行仿真验证,如图4 所示为baud_set=5时的仿真结果。由仿真结果可知,发送时钟uart_tx_clk 持续输出;

当rx_in_reg=1时,启动接收时钟uart_rx_clk 的输出,当receive_done=1时,关闭接收时钟的输出。

图4 UART_CLk 模块仿真结果Figure 4 UART_ CLk module simulation results

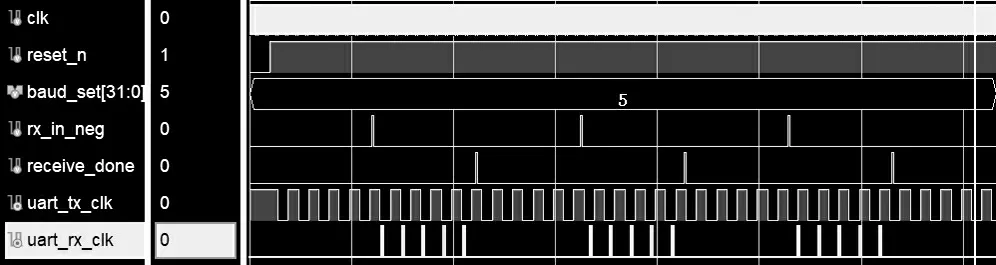

2.4 FIFO 设计

为了解决在发送的过程中CPU 输出数据的速度与UART 传送数据的速度不匹配的问题,需要设计发送FIFO(TX_FIFO)。在发送的过程中,CPU 只需通过LocalIO 总线向TX_FIFO 中写入数据,当TX_FIFO 不为空时,TX_FIFO 中的数据就会被UART_TX 模块自动发送出去,直到TX_FIFO 空为止。在接收数据的过程中,如果没有接收FIFO,则串口每接收完一个数据后,FPGA 就会产生一次接收中断输出,如果进行大量数据的持续传输,则会导致CPU 一直进入中断,造成CPU 死机。为了避免在数据接收过程中的频繁中断问题,需要在接收侧设计接收FIFO(RX_FIFO)。在该UART IP 核中,TX_FIFO 与RX_FIFO 的容量设计为256Byte,FIFO使用Xilinx 自带的IP 核实现。TX_FIFO 自动发送与RX_FIFO 自动接收的状态机设计,如图5 所示。

图5 FIFO 读写控制状态机a)TX_FIFO 自动发送状态机;

b)RX_FIFO 自动接收状态机Figure 5 FIFO read and write control state machine a)TX_FIFO automatic receiving state machine b)RX_FIFO automatic transmission machine

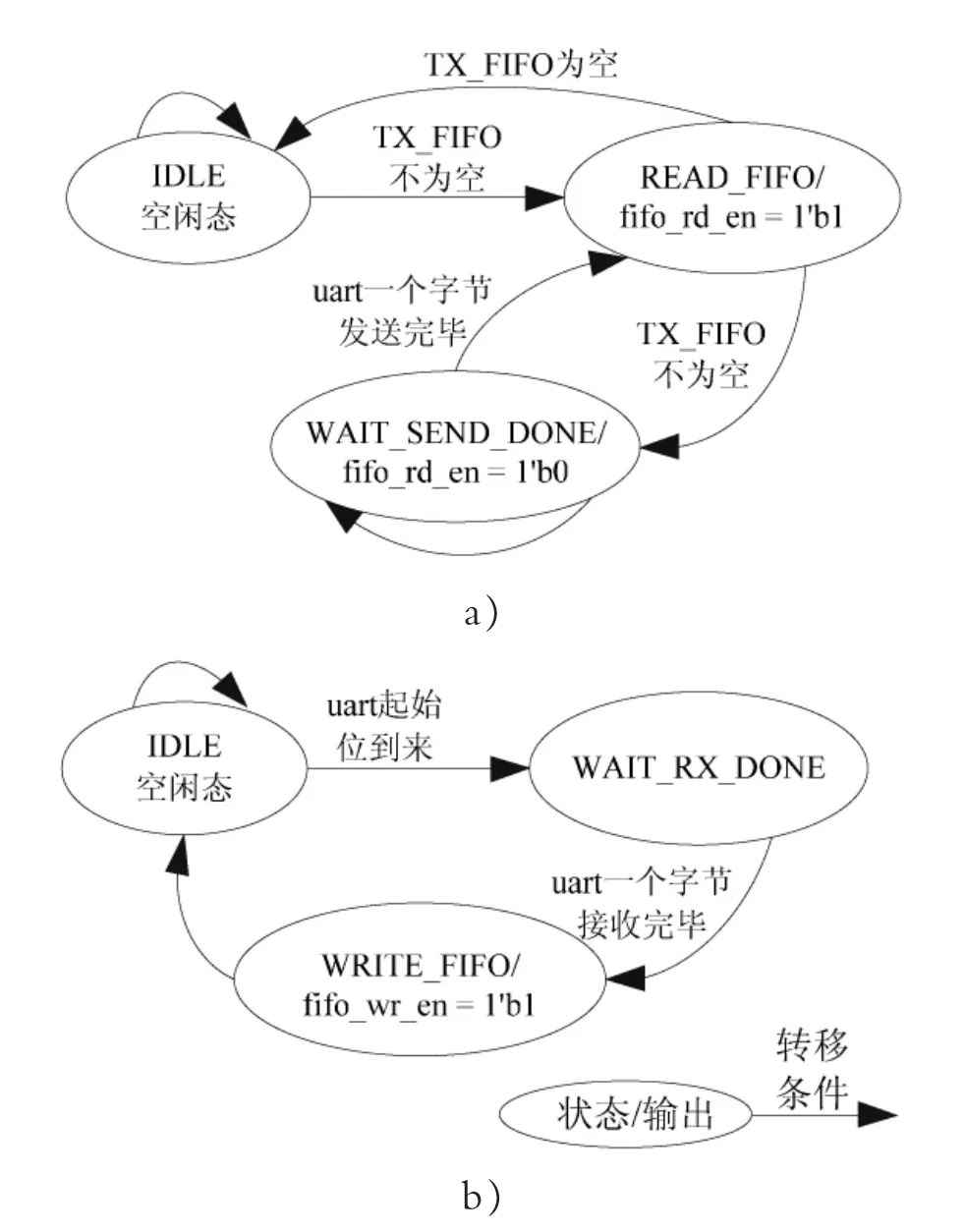

2.5 中断系统设计

一个系统是否具有中断功能,决定了该系统对外部资源的消耗情况以及该系统的兼容性。如果一个系统没有中断功能,则需要消耗大量的CPU 资源去查询该系统的当前状态,同时也会降低该系统的对外兼容性。为了降低UART IP 核对CPU 资源的消耗,提高串口通信的实时性,该UART IP 核设计了接收中断系统[6],该接收中断具有阈值机制与超时机制。阈值机制的功能是:当接收数据的字节个数小于设定的阈值时,不产生中断;

当接收数据的字节数大于设定的阈值后,产生中断,它可用于基于串口帧的自定义通信协议中断适配。超时机制用于在通信的过程中接收数据一直无法达到设定阈值进而无法正常产生中断,导致中断一直无法输出的情况。该UART IP 核的中断系统由中断寄存器与中断控制逻辑两部分组成。中断寄存器包括中断使能寄存器、中断状态寄存器、阈值配置寄存器、超时配置寄存器。中断控制的处理逻辑如图6 所示。该中断采用电平的方式输出,并且具有自动清除中断的功能。当UART IP 核的接收中断产生时,中断输出引脚置为高电平,当CPU 读取RX_FIFO 中的数据后中断输出自动清除,同时中断状态寄存器的相应标志位自动清零,不需要CPU 手动清除中断标志。

图6 中断生成控制流程Figure 6 Control flow of interrupt generation

2.6 配置模块设计

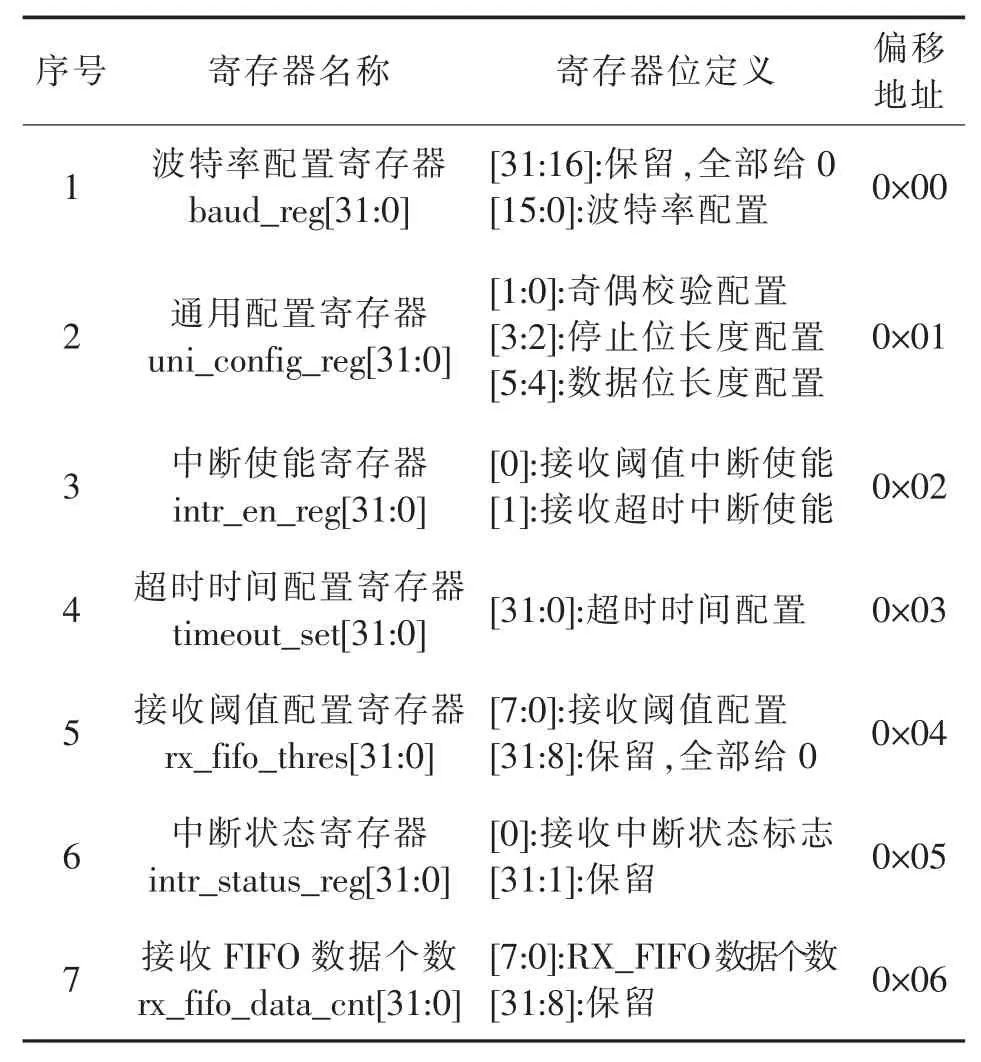

为了使FPGA 运行过程中CPU 能够在线对UART IP 核的参数进行配置[7],设计了独立的配置模块(UART_ CONFIG 模块),用于保存UART IP核的各种配置参数。配置模块由各种配置寄存器构成,CPU 通过Local IO 接口可以对这些寄存器进行读写操作。配置参数主要包括UART 协议基本配置参数、中断配置参数等[8]。配置模块的寄存器详细设计如表1 所示。

表1 寄存器名称、含义及访问地址Table 1 Register name,meaning and access address

2.7 Local IO 接口模块设计

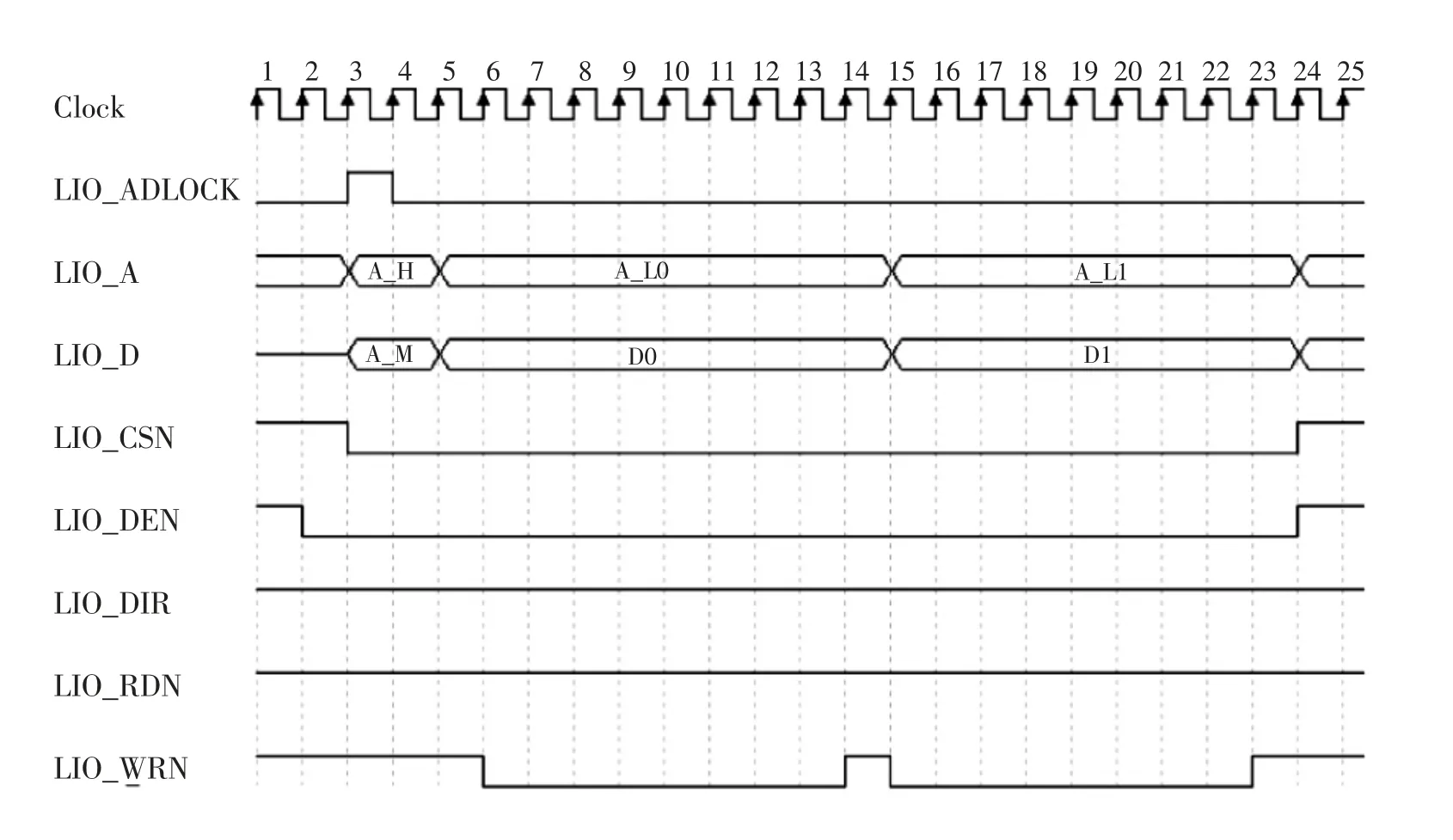

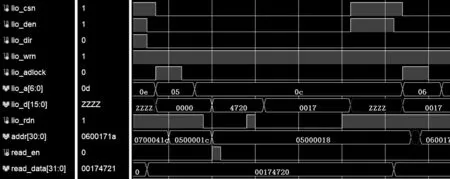

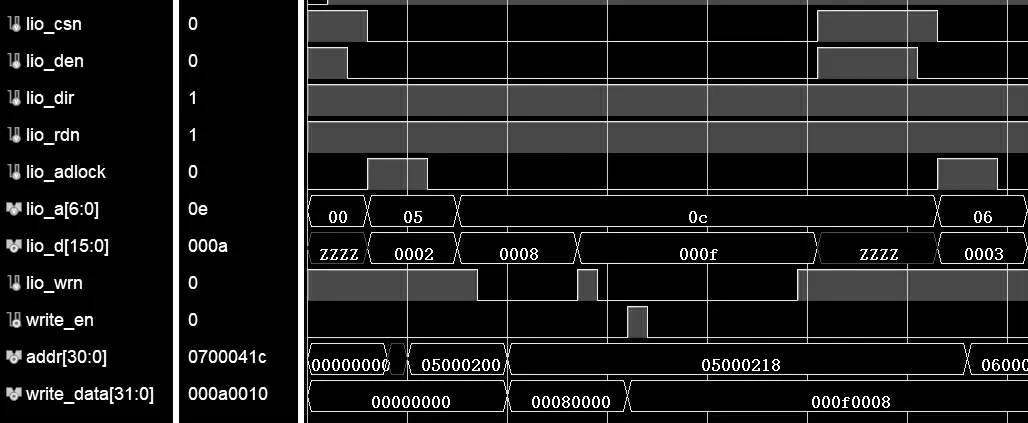

Local IO 处理模块用于实现UART IP 核与龙芯CPU Local IO 接口的适配。龙芯Local IO 接口的读时序如图7 所示,写时序如图8 所示。按照Local IO 的驱动时序,编写Local IO 的驱动,并对读写驱动进行仿真,其结果分别如图9 和图10 所示,由仿真结果可知读写驱动时序正确。

图7 Local IO 读时序Figure 7 Local IO read timing

图8 Local IO 写时序Figure 8 Local IO write timing

图9 Local IO 读数据仿真结果Figure 9 Local IO read data simulation results

图10 Local IO 写数据仿真结果Figure 10 Local IO write data simulation results

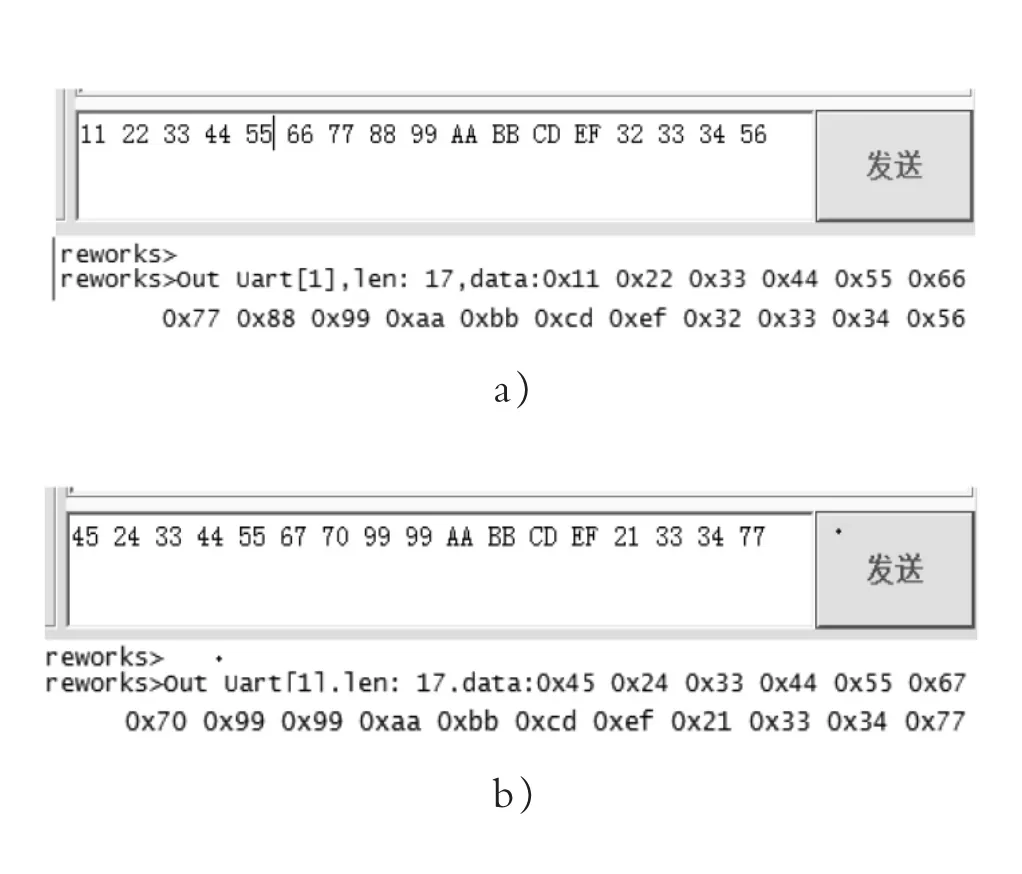

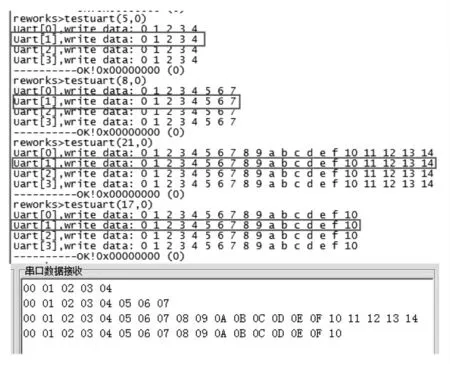

为了验证UART IP 核设计的正确性,将程序下载到FPGA中[9-10]。首先测试UART IP 核的接收功能,利用串口调试助手向FPGA 的一号通道发送数据,FPGA 收到数据后产生中断,并通过Local IO接口将数据发送给龙芯CPU,龙芯CPU 读取数据并打印出读取的结果,随机抽取两组测试结果如图11 所示,每组结果中上方为串口调试助手发送的数据,下方为CPU 接收的数据。由结果可知,功能正确。接着测试UART IP 核的发送功能,龙芯CPU通过Local IO 接口向FPGA 的1 号通道发送数据,FPGA 收到数据后将数据发送给串口调试助手,随机抽取4 组数据,其结果如图12 所示。图12 中上方为CPU 发送的数据,下方为串口调试助手接收的数据。由图12 可知,发送与接收的数据一致,表明设计正确。

图11 串口数据接收测试结果a)测试结果1 b)测试结果2Figure 11 Serial port data receiving test result a)test result 1 b)test result 2

图12 串口数据发送测试结果Figure 12 Serial port data transmission test results

本文根据龙芯CPU Local IO 接口的特点,设计了适配Local IO 接口的UART IP核,解决了龙芯CPU 通过FPGA 扩展UART 接口的需求。在设计时采用模块化设计的思想,增强了IP 核的可裁剪性。在设计中断系统时引入接收阈值机制与接收超时机制,避免频繁产生中断的现象发生,提高了IP 核与CPU 的兼容性,增强了龙芯CPU 在设计中的普适性。该IP 核在Vivado 中综合实现后,消耗的资源情况为:LUT 1212个,LUTRAM 26个,FF 1822个,BRAM 1 个。

猜你喜欢龙芯波特率寄存器基于国产化龙芯的动环数据采集系统中国交通信息化(2022年9期)2022-10-28STM32和51单片机寄存器映射原理异同分析有色金属设计(2022年4期)2022-02-04CAN 总线波特率自适应程序设计智能制造(2020年5期)2020-07-03Lite寄存器模型的设计与实现计算机应用(2020年5期)2020-06-07“龙芯之父”胡伟武华人时刊(2016年13期)2016-04-05龙芯发布新一代处理器产品信息安全与通信保密(2015年9期)2015-11-02C*Core芯片SCI串口波特率容限优化电子设计工程(2012年3期)2012-07-13高速数模转换器AD9779/AD9788的应用网络安全与数据管理(2011年24期)2011-08-08UART波特率发生电路设计电子与封装(2010年9期)2010-09-05一种可重构线性反馈移位寄存器设计通信技术(2010年8期)2010-08-06